基于FPGA的乐曲演奏器的设计

无需注册登录,支付后按照提示操作即可获取该资料.

基于FPGA的乐曲演奏器的设计(任务书,开题报告,论文9000字)

摘 要

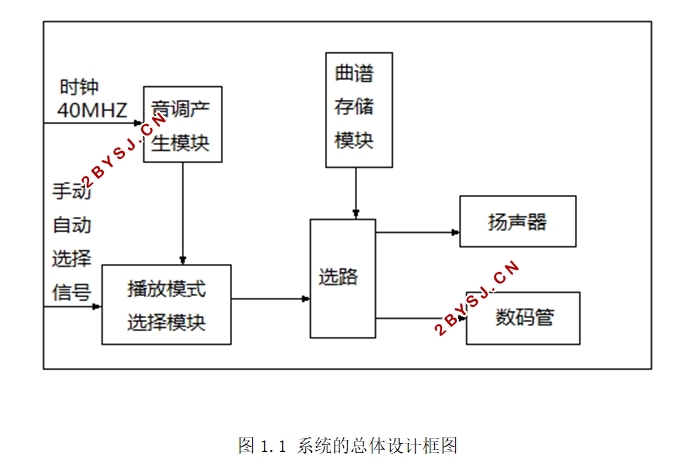

本文主要阐述的是基于EDA技术,设计一个乐曲演奏器。该乐曲演奏器是基于数控分频的原理。在系统时钟为40MHZ的基础上,进行数控分频以此达到音调和音色产生的效果。该乐曲演奏器可以通过手动进行按键输入来控制演奏也可以自动播放已经定制好的乐曲。乐曲演奏器的设计是在原有普通电子琴的基础上进行的一个扩充设计。该演奏器主要由5大模块组成,分别是分频模块,播放模式选择模块,曲谱存储模块,显示模块和扬声器驱动。在进行设计的时候使用的描述语言是超高速硬件描述语言verilog HDL,通过编程来实现各个模块的功能。系统按照模块化方式进行设计,然后进行编程,时序仿真最后进行总体的整合。本设计功能齐全,并且具有一定的现实实现价值。此次设计在xilinx ise软件上进行编程,使用modelsim软件进行时序仿真。最终将实现好的程序下载到xilinx公司的开发板XC3S500里面从而完成整个设计。

关键字:乐曲演奏,verilog HDL,FPGA,xilinx ise

Music player based on VHDL

Abstract

The main contents of this paper are for a music player system design .The theory of this design is depend on frequency division of computer .The clock of the system is 40MHZ。The music player has two function: Automatic play the song or Manua play the song by key input just like a piano.This mucic player system is composed by frequency Divider circui,Select module,Internal ROM,Manual / automatic routing module,Digital display and speaker.We achieve the function of each module by using Ultra-high-speed hardware description language Verilog programming.It can play music automatically or play music manually.The system uses a hardware description language Verilog to design in a modular way, and then be programmed timing simulation, then the overall integration.The function of the system is relatively complete, and there is a certain reality to realize the value. The design is above the Xilinx ise software programming, timing simulation using modelsim software. And eventually the achieved program will be downloaded to the Xilinx development board XC3S500E.

Keywords: music player system; verilog; FPGA; xilinx ise

目录

摘 要 I

Abstract II

第一章 绪论 1

1.1研究背景 1

1.2课题内容 2

1.3方案比较 2

1.4具体方案 3

第二章 乐曲演奏器的设计 5

2.1乐曲演奏器的设计原理 5

2.2音调产生模块 6

2.2.1音调的控制 6

2.2.2音长的控制 7

2.3播放模式选择模块 8

2.4曲谱存储模块 10

2.5显示模块 12

2.6扬声器驱动模块 13

2.7顶层模块设计 14

2.8时序仿真 16

第三章 硬件调试 18

3.1开发板应用模块介绍 18

3.2调试过程 19

3.2.1引脚锁定 19

3.2.2程序下载 19

第四章 总结 21

参考文献 22

致谢 23

附录 24