基于FPGA的多功能信号发生器设计

无需注册登录,支付后按照提示操作即可获取该资料.

基于FPGA的多功能信号发生器设计(论文12000字)

摘要:本设计实现了一种能够产生多种信号的多功能发生器。本设计共有三个模块,分别是信号源,FPGA模块和网络接口板。本设计的优点就在于利用了FPGA内部有锁相环,能够对外部时钟进行倍频,且工作频率能达到几百兆,而且本设计不是采用传统的按键控制,而是通过上位机中对程序的改变来改变相应的幅度、相位、偏置和频率以及程序中对所设定的关于各种波形所对应的值的改变,从而产生多种谐波率较低,频率范围为1HZ到100M的正弦波,方波,三角波等多种波形。

关键字:DDS,FPGA,以太网,多功能信号发生器,上位机

Multifunctional signal generator based on FPGA

Abstract:The design implements a multi-purpose generator which can produce a variety of signals.The design consists of three modules.They are signal source, FPGA module and the network interface board.Advantages of this design is that the use of the FPGA internal PLL which can the external clock frequency, and the operating frequency can reach hundreds of megabytes.The design changes the corresponding amplitude, phase, offset, frequency and value change for various waveforms corresponding to the set by the host computer resulting in a variety of low harmonics, frequency range for a variety of waveforms 1HZ to 100M sine, square, triangle and so on.

Key words: DDS,FPGA,Ethernet,Multifunctional signal generator,computer

目 录

论文总页数:41页

引言 5

1.课题背景 5

2. 国内外波形发生器的发展现状 6

3.本文研究的主要内容 6

4. 设计内容 6

1.信号发生器原理 6

1.1直接数字频率合成技术的基本原理 7

1.1.1 DDS的原理 7

1.1.1 DDS的优缺点 7

1.1.2 DDS的实现 8

1.2相位偏移控制 8

2.硬件部分 9

2.1系统设计 9

2.2 下位机系统 9

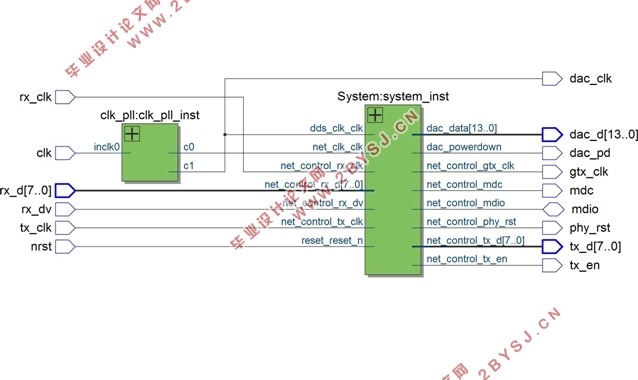

2.2.1 FPGA模块 9

2.2.2 网络接口板 14

2.2.3 信号源模拟前端 14

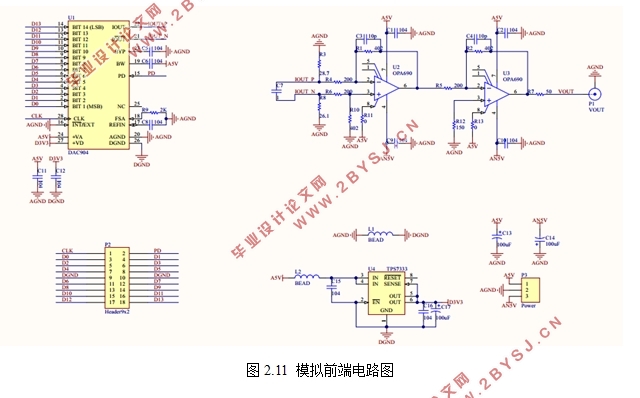

2.2.4 模拟前端电路图 17

2.2.5 硬件实物连接图 18

3.软件 19

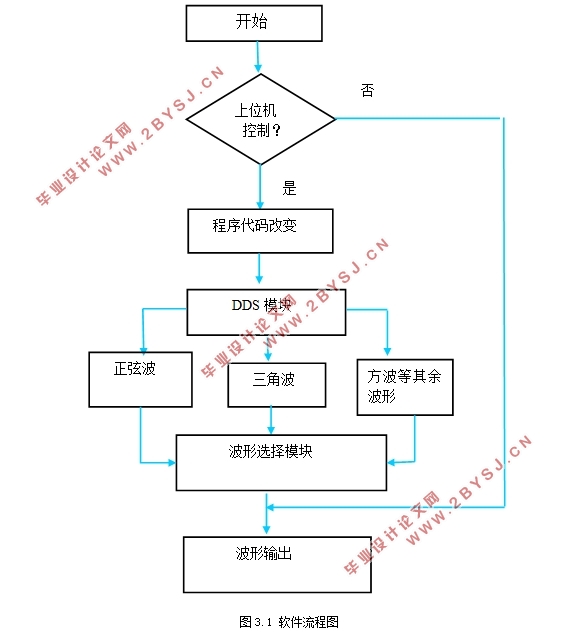

3.1 软件流程图 19

3.2系统设计 20

3.2.1 系统初始化模块 20

3.2.2 RAM模块 20

3.2.3 数据转换模块 20

3.2.4 DAC驱动模块 21

3.2.5 信号发生器模块 22

3.3 上位机模块 27

4.实验结果与结论 28

4.1 实验图 28

4.2 实验结论 30

5.附录 31

5.1 实物图 31

5.2 控制D/A代码 32

5.3 FPGA内部电路图 36

参考文献 40

致谢 41