基于FPGA的多通道采样系统设计(附程序,电路图,PCB图)

无需注册登录,支付后按照提示操作即可获取该资料.

基于FPGA的多通道采样系统设计(附程序,电路图,PCB图)(开题报告,中期报告,外文翻译,论文24000字)

本论文介绍了基于FPGA的多通道采样系统的设计。用FPGA设计一个多通道采样控制器,利用VHDL语言设计有限状态机来实现对AD7892的控制。由于FPGA器件的特性是可以实现高速工作,为此模拟信号选用音频信号。由于音频信号的频率是20Hz-20KHz,这样就对AD转换的速率有很高的要求.因为FPGA的功能很强大,所以我们把系统的许多功能都集成到FPGA器件中,例如AD通道选择部分,串并输出控制模块,这样使得整个系统的外围电路简单、系统的稳定性强。FPGA的配置模式选用被动串行模式,这样就增强了系统的可扩展性。输出模式可选择性使得系统的应用相当广泛,串行输出可以用于通信信号的采集,方便调制后发射到远程接受端,远程接收端对采集的数据进行解调;而并行输出模式则可以通过高速存储器将采集的信号放到微机或者其他的处理器上,根据采集的数据进行相应的控制。此系统的缺点是由于FPGA器件配置是基于SRAM查找表单元,编程的信息是保持在SRAM中,但SRAM在掉电后编程信息立即丢失,所以每次系统上电都需要重新配置芯片,这对在野外作业的工作人员很不方便,解决的方法是专用的配置器件来配置FPGA,在每次系统上电的时候会自动把编程信息配置到FPGA芯片中。但设计中没有采用到这种配置方案主要是考虑到专用配置器件的价格问题。

本文开始介绍了多通道系统的组成部分,然后分别介绍了各个组成部分的原理和设计方法,其中重点介绍了FPGA软件设计部分。还对当前十分流行的基于FPGA的设计技术作了简单的阐述,最后对系统的调试和应用作了简短的说明。

目 录

引言•••••••••••••••••••••••••••••••••••••••••••••••••••••••••••1

1 FPGA和VHDL概述•••••••••••••••••••••••••••••••••••••••••••••1

FPGA发展历程•••••••••••••••••••••••••••••••••••••••••••••••••1

VHDL语言介绍•••••••••••••••••••••••••••••••••••••••••••••••••3

2 多通道采样系统的组成••••••••••••••••••••••••••••••••••••••••3

3 总体方案设计与论证••••••••••••••••••••••••••••••••••••••••••4

3.1 方案设计•••••••••••••••••••••••••••••••••••••••••••••••••••••4

3.1.1方案一•••••••••••••••••••••••••••••••••••••••••••••••••••••4

3.1.2方案二•••••••••••••••••••••••••••••••••••••••••••••••••••••4

3.1.3方案三•••••••••••••••••••••••••••••••••••••••••••••••••••••4

3.2方案比较•••••••••••••••••••••••••••••••••••••••••••••••••••••4

4 单元电路的设计••••••••••••••••••••••••••••••••••••••••••••••5

4.1音频放大、滤波部分••••••••••••••••••••••••••••••••••••••••••••5

4.1.1音频放大部分••••••••••••••••••••••••••••••••••••••••••••••••5

4.1.2有源滤波器的设计•••••••••••••••••••••••••••••••••••••••••••••6

4.2 AD采样电路•••••••••••••••••••••••••••••••••••••••••••••••••••8

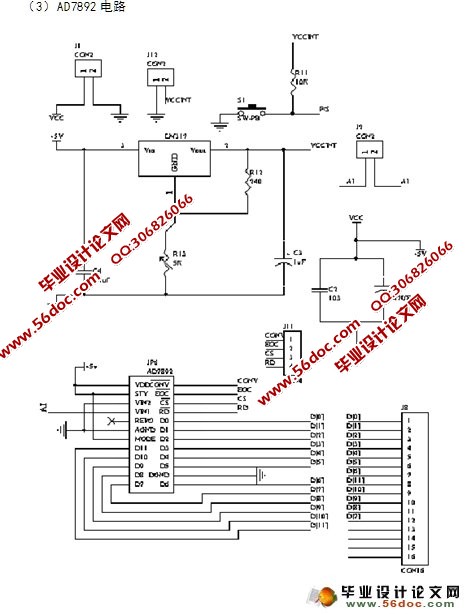

4.2.1芯片介绍••••••••••••••••••••••••••••••••••••••••••••••••••••8

4.2.2芯片应用•••••••••••••••••••••••••••••••••••••••••••••••••••11

4.3 FPGA控制部分•••••••••••••••••••••••••••••••••••••••••••••••••11

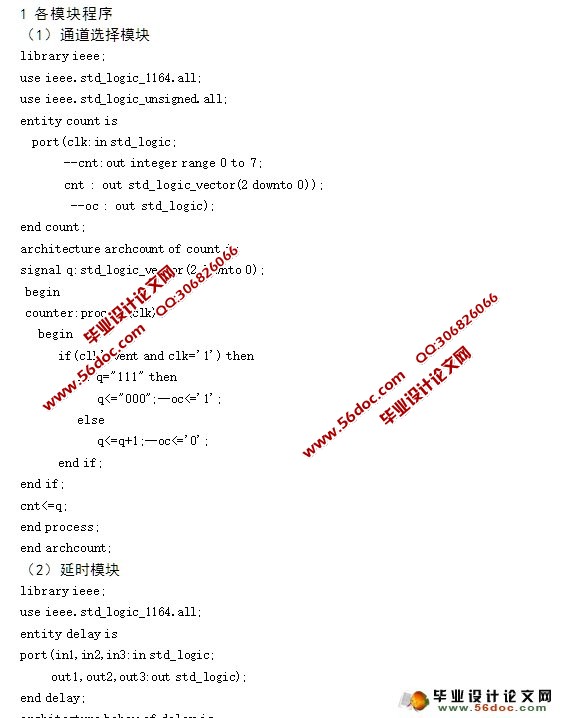

4.3.1通道选择模块•••••••••••••••••••••••••••••••••••••••••••••••11

4.3.2 AD7892控制部分•••••••••••••••••••••••••••••••••••••••••••••12

4.3.3延时模块的设计•••••••••••••••••••••••••••••••••••••••••••••17

4.3.4串并输出选择控制••••••••••••••••••••••••••••••••••••••••••••18

4.3.5 FIFO模块••••••••••••••••••••••••••••••••••••••••••••••••••18

4.3.6 AD采样系统顶层电路设计••••••••••••••••••••••••••••••••••••••19

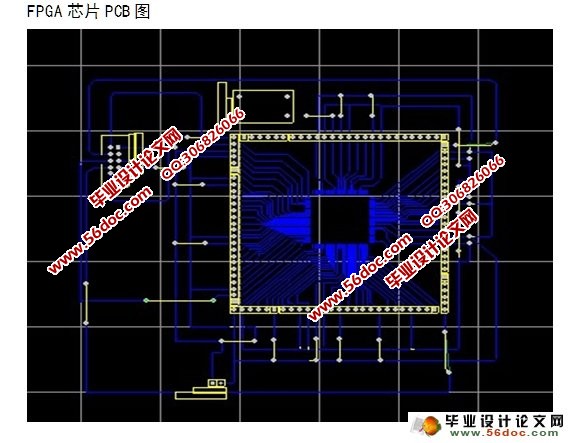

4.4 FPGA的硬件设计••••••••••••••••••••••••••••••••••••••••••••••20

4.4.1 EP1K30TC144-3芯片介绍•••••••••••••••••••••••••••••••••••••••20

4.4.2芯片组成描述•••••••••••••••••••••••••••••••••••••••••••••••20

4.4.3芯片工作电压设计••••••••••••••••••••••••••••••••••••••••••••21

4.4.4芯片配置介绍•••••••••••••••••••••••••••••••••••••••••••••••22

4.4.5电路设计注意事项••••••••••••••••••••••••••••••••••••••••••••24

4.4.6硬件电路设计技巧••••••••••••••••••••••••••••••••••••••••••••25

5 软件介绍•••••••••••••••••••••••••••••••••••••••••••••••••••25

5.1 MAX+PlusⅡ••••••••••••••••••••••••••••••••••••••••••••••••••25

5.2 Electronics Workbench(EWB) ••••••••••••••••••••••••••••••••••••25

5.3Protel99SE•••••••••••••••••••••••••••••••••••••••••••••••••••26

6 整机调试•••••••••••••••••••••••••••••••••••••••••••••••••••26

6.1 硬件电路的调试步骤•••••••••••••••••••••••••••••••••••••••••••26

6.1.1音频放大部分调试••••••••••••••••••••••••••••••••••••••••••••26

6.1.2滤波部分调试•••••••••••••••••••••••••••••••••••••••••••••••27

6.1.3LM317稳压块调试•••••••••••••••••••••••••••••••••••••••••••••27

6.1.4FPGA硬件电路调试••••••••••••••••••••••••••••••••••••••••••••27

6.1.5AD采样模块调试••••••••••••••••••••••••••••••••••••••••••••••28

6.2 联机调试••••••••••••••••••••••••••••••••••••••••••••••••••••28

6.3调试注意事项•••••••••••••••••••••••••••••••••••••••••••••••••28

7 结论•••••••••••••••••••••••••••••••••••••••••••••••••••••••29

谢辞••••••••••••••••••••••••••••••••••••••••••••••••••••••••••30

参考文献••••••••••••••••••••••••••••••••••••••••••••••••••••••31

附录••••••••••••••••••••••••••••••••••••••••••••••••••••••••••32