测量仪器-数字频率计的设计(Max+plusⅡ仿真)

无需注册登录,支付后按照提示操作即可获取该资料.

数字频率计是一种基本的测量仪器。它被广泛应用与航天、电子、测控等领域。它利用VHDL硬件描述语言进行设计,并在EDA(电子设计自动化)工具的帮助下,用大规模可编程器件(CPLD)实现数字频率计的设计原理及相关程序。通过了Max+plusⅡ软件进行仿真、硬件调试和软硬件综合测试特点是:无论底层还是顶层文件均用VHDL(硬件语言)语言编写,避免了用电路图设计时所引起的毛刺现象;改变了以往数字电路小规模多器件组合的设计方法。整个频率计设计在一块CPLD芯片上,与用其他方法做成的频率计相比,体积更小,性能更可靠。

关键词 数字频率计 EDA CPLD

Digital frequency of design

Abstract

The number of frequencies is a basic measuring instruments. It is widely used and aerospace, electronics, monitoring and control, and other fields. It uses VHDL hardware description language design and EDA (electronic design automation) tools help, with large-scale programmable devices (CPLD) to achieve digital frequency of the design principle and the relevant procedures. By the Max + plus Ⅱ simulation software, hardware debug and test integrated hardware and software features are: whether the top or bottom of documents with VHDL (hardware language) languages, designed to avoid the use circuit caused by the burr; change the past Digital circuit small-scale multi-device combination of design methods. The frequency of design in a CPLD chip, and by other means made of the frequency compared to smaller, more reliable performance

Key Words Digital frequency of design EDA CPLD

频率计是数字电路中的典型器件,其实现的方法,选用的器件也是多种多样的。本次虽然也是频率计的设计,单采用了ISP技术。用CPLD来实现,是对典型电路的一个新型设计方法的尝试。这个设计过程无不体现:正是由于ISP技术的优越性,使整个系统从最初方案的设计到编写程序。从仿真调试到下载试验,都显得相当快捷和方便。采用ISP技术有简化生产流程且无引脚损伤,实现多功能硬件,为进行测试而重构逻辑等优点。另外,正是因ISP技术使硬件设计“软件化”了,对系统的维护和现场开发只是凭借一张磁盘就能实现,而这在常规逻辑技术下几乎是不可能的。随着网络技术的日益完善。通过网络来对远隔万里的用户系统进行软件版本升级换代,将给厂家与用户带来更多方便。

本设计所介绍的数字频率计是一个简易频率计,只能测量10K~9.9MHz之间的频率,并且对于低频和高频具有不同测量精度。这样的频率计是不能用于实际频率测量的。

但是在这里只是为了介绍自顶向下的设计方法。我们从数字频率计的层次图可以看出,不同模块有不同的层次级别,模块越复杂,层次越多。在不同模块之间是相互独自的,但底层模块的修改不会影响其他模块的工作,采用这种设计方法的设计结构清晰、层次清楚,便于对设计进行修改。

在这次毕业设计中,我不仅是在知识得到很多收获,更多是在精神上得到很多启示。从得到设计题目,到查阅资料,最后到书写设计,其中每一步都有很多感受,使我明白做学问不容易,需要智慧,需要勇气,还需要毅力。我将把这种精神用在今后的学习、工作中,一定会在将来的事业中取得满意的成绩。

绪论

CPLD是一种新兴的高密度大规模可编程逻辑器件,它具有门阵列的高密度和PLD器件的灵活性和易用性,目前已成为一类主要的可编程器件。可编程器件的最大特点是可通过软件编程对其器件的结构和工作方式进行重构,能随时进行设计调整而满足产品升级。使得硬件的设计可以如软件设计一样方便快捷,从而改变了传统数字系统及用单片机构成的数字系统的设计方法、设计过程及设计概念,使电子设计的技术操作和系统构成在整体上发生了质的飞跃。

采用CPLD可编程器件,可利用计算机软件的方式对目标期进行设计,而以硬件的形式实现。既定的系统功能,在设计过程中,可根据需要随时改变器件的内部逻辑功能和管脚的信号方式,借助于大规模集成的CPLD和高效的设计软件,用户不仅可通过直接对芯片结构的设计实现多种数字逻辑系统功能,而且由于管脚定义的灵活性,大大减轻了电路图设计和电路板设计的工作量及难度,同时,这种基于可编程芯片的数量,缩小了系统的体积,提高了系统的可靠性。EDA(电子设计自动化)技术就是以计算机为工具,在EDA软件平台上,对硬件语言HDL为系统逻辑描述手段完成的设计文件,自动的完成逻辑编译、逻辑化简、逻辑综合及优化、逻辑仿真,直至对特定目标芯片的适配编译、逻辑映射和编程下载等工作(文本选用的开发工具为Altera公司的MAX+PLUSII)。EDA的仿真测试技术只需要通过计算机就能对所设计的电子系统从各种不同层次的系统性能特点完成一系列准确的测试与仿真操作,大大提高了大规模系统电子设计的自动化程度。设计者的工作仅限于利用软件方式,即利用硬件描述语言(如VHDL)来完成对系统硬件功能的描述。

VHDL语言(Very High Speed Integrated Circuit Hardware Description Language,超高速集成电路硬件描述语言)诞生于1982年,是由美国国防部开发的一种快速设计电路的工具,目前已成为IEEE(The Institute of Electrical and Electronics Engineers)的一种工业标准硬件描述语言,相比传统的电路系统的设计方法,VHDL具有多层次描述系统硬件功能的能力,支持自顶向下(Top to Down)和基于库(Library-based)的设计的特点,因此设计者可以不必了解硬件结构设计,

目 录

1 绪论 …………………………………………………………………………………3

2 CPLD简介……………………………………………………………………………4

2.1 CPLD器件的基本结构……………………………………………………………4

2.2典型CPLD器件简述………………………………………………………………7

2.3 CPLD的编程工艺…………………………………………………………………8

2.4新技术的应用…………………………………………………………………… 9.

3 MAX+PLUSⅡ软件的介绍………………………………………………………… 10.

3.1 MAX+PLUSⅡ的概述…………………………………………………………… 10

3.2 MAX+PLUSⅡ的功能简介……………………………………………………… 10

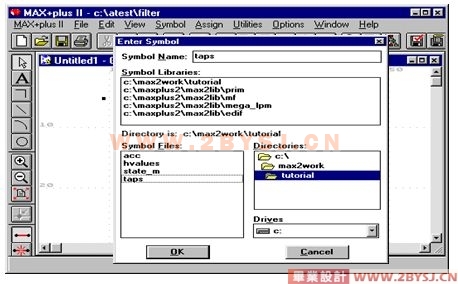

3.3 MAX+PLUSⅡ的应用…………………………………………………………… 11

4 数字频率计的设计目的……………………………………………………………14

5 数字频率计的设计原理……………………………………………………………15

(优秀毕业设计:www.2bysj.cn)

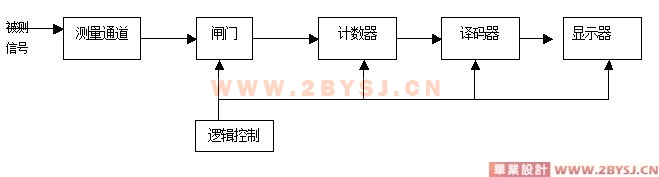

5.1 数字频率计的基本组成…………………………………………………………15.

5.2 数字频率计的分类………………………………………………………………16

5.3 数字频率计的计数指标…………………………………………………………16

5.4数字频率计的基本工作原理…………………………………………………… 16

5.5 数字频率计技术指标及误差分析………………………………………………17

6 数字频率计的设计…………………………………………………………………18

6.1 数字频率计设计任务及要求……………………………………………………18

6.2 设计实现…………………………………………………………………………18

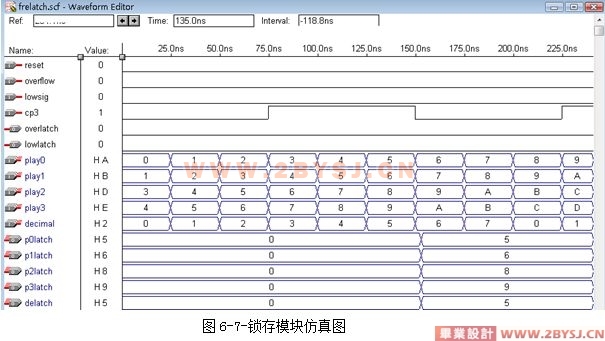

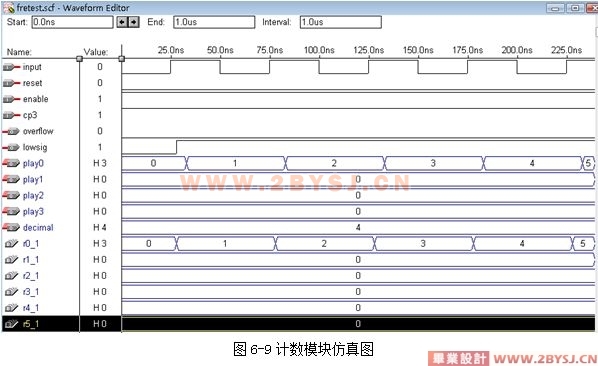

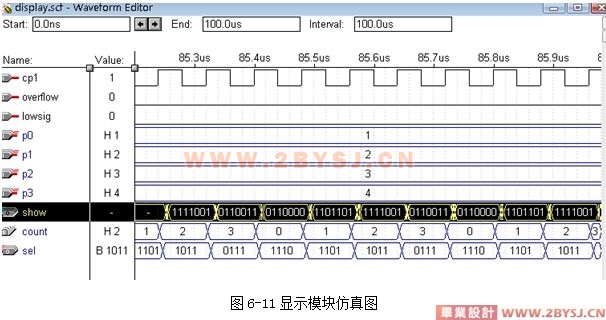

6.3 功能模块设计……………………………………………………………………19

6.4 各模块基于VHDL的设计方法………………………………………………… 19

6.5 顶层文件的编写…………………………………………………………………33

6.6 程序说明…………………………………………………………………………36

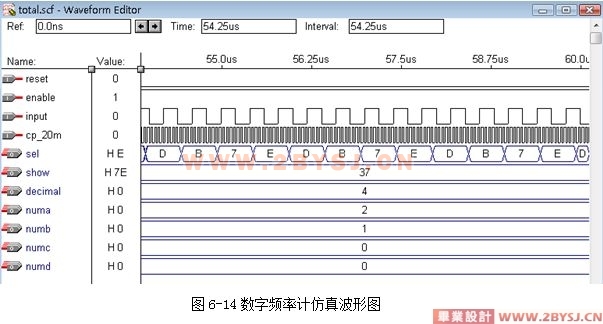

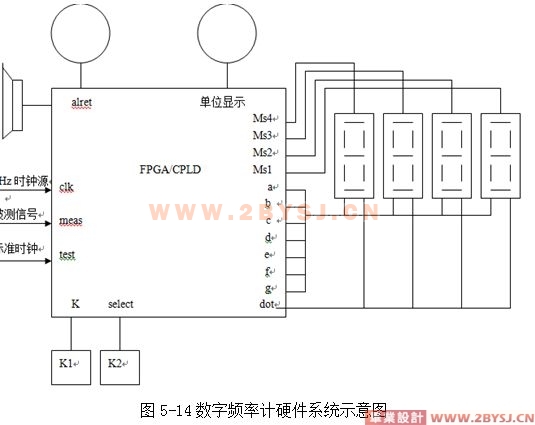

6.7系统仿真…………………………………………………………………………36

6.8下载验证…………………………………………………………………………36

7 结束语………………………………………………………………………………37

致谢……………………………………………………………………………………38

参考文献………………………………………………………………………………39

参考文献

1 杨刚,龙海燕.现代电子技术――VHDL与数字系统设计[M].北京:电子工业出版社,2004

2 顾斌,赵明忠,姜志鹏,马才根.数字电路EDA设计.西安[M].西安电子科技大学出版社,2004

3 王道宪.CPLD/FPGA可编程器件应用与开发[M].北京:国防工业出版社,2003

4 谢煌,黄为.基于VHDL语言设计频率计[J].北京:现代电子技术,2003,14

5 武卫华,陈德宏.基于EDA技术的数字频率计芯片化的实现[J].电测与仪表,2004,4

6 卢毅等,VHDL与数字电路设计[M].北京:科学院,2001

更多电子毕业设计毕业论文

http://www.papersay.com/Machine_electron/

/Electronics/

http://www.doc163.com/mechatronics/

7 潘松,VHDL实用教程[M].成都:电子科技大学出版社,2000

8 徐志军,大规模可编程逻辑器件及其应用[M].成都:电子科技大学出版社,2000

9 候伯华,数字系统设计基础[M].西安电子科技大学出版社,2000

10 张亦华等.数字电路EDA入门---VHDL程序实例集[M].北京:北京邮电大学出版社,2003